# **CMOS MT9D111Camera Module**

## 1/3.2-Inch 2-Megapixel Module Datasheet

Rev 1.0, Mar 2013

#### 2 M Pixels CMOS MT9D111 CAMERA MODULE

#### **Table of Contents**

| 1 | Introduction         | 2 |

|---|----------------------|---|

| 2 | Features             | 2 |

|   | Block Diagram        |   |

| 4 | Application          | 4 |

| 5 | Pin Definition       | 6 |

| 6 | Mechanical Dimension | 7 |

#### 1 Introduction

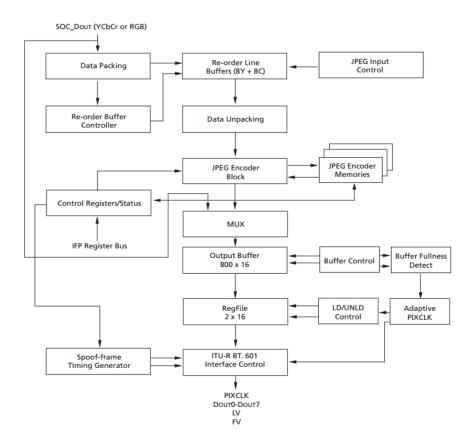

Micron® Imaging MT9D111 is a 1/3.2 inch 2-megapixel CMOS image sensor with an integrated advanced camera system. The camera system features a microcontroller (MCU) and a sophisticated image flow processor (IFP) with a real-time JPEG encoder. It also includes a programmable general purpose I/O module (GPIO), which can be used to control external auto focus, optical zoom, or mechanical shutter.

The microcontroller manages all components of the camera system and sets key operation parameters for the sensor core to optimize the quality of raw image data entering the IFP. The sensor core consists of an active pixel array of 1668 x 1248 pixels, programmable timing and control circuitry including a PLL and external flash support, analog signal chain with automatic offset correction and programmable gain, and two 10-bit A/D converters (ADC). The entire system-on-a-chip (SOC) has ultra-low power requirements and superior low-light performance that is particularly suitable for mobile applications.

The excellent low-light performance of MT9D111 is one of the hallmarks of DigitalClarity<sup>TM</sup>—Micron's breakthrough low-noise CMOS imaging technology that achieves CCD

image quality (based on signal-to-noise ratio and low-light sensitivity) while maintaining the inherent size, cost, power consumption, and integration advantages of CMOS.

## 2 Features

| Paramet           | er       | Value                                              |

|-------------------|----------|----------------------------------------------------|

| Optical format    |          | 1/3.2-inch (4:3)                                   |

| Full resolution   |          | 1,600 x 1,200 pixels (UXGA)                        |

| Pixel size        |          | 2.8µm x 2.8µm                                      |

| Active pixel arra | ay area  | 4.73mm x 3.52mm                                    |

| Shutter type      |          | Electronic rolling shutter (ERS) with global reset |

| Maximum fram      | e rate   | 15 fps at full resolution,                         |

|                   |          | 30 fps in preview mode,                            |

|                   |          | (800 x 600)                                        |

| Maximum data      | rate/    | 80 MB/s                                            |

| master clock      |          | 6 MHz to 80 MHz                                    |

|                   | Analog   | 2.5V-3.1V                                          |

| Supply voltage    | Digital  | 1.7V-1.95V                                         |

|                   | 1/0      | 1.7V-3.1V                                          |

|                   | PLL      | 2.5V-3.1V                                          |

| ADC resolution    |          | 10-bit, on-die                                     |

| Responsivity      |          | 1.0/lux-sec (550nm)                                |

| Dynamic range     |          | 71dB                                               |

| SNRMAX            |          | 42.3dB                                             |

|                   |          | 348mW at 15 fps, full resolution                   |

| Power consump     | otion    | 223mW at 30 fps, preview mode                      |

| Operating temp    | perature | -30°C to +70°C                                     |

| Package           |          | Bare die, 64-ball iCSP                             |

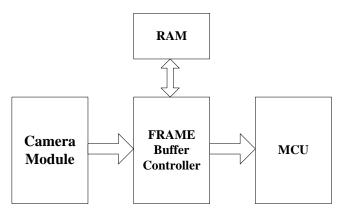

#### 3 Diagram

#### 4 Application

- Cellular phones

- PDAs

- > Toys

- Other battery-powered products

- > Can be used in Arduino, Maple, ChipKit, STM32, ARM, DSP, FPGA platforms

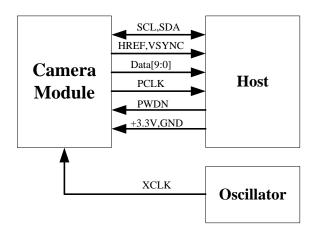

The following schematic diagram show a basic camera based system. The camera module is powered from a single +3.3V power supply. An external oscillator provide the clock source for camera module XCLK pin. With proper configuration to the camera internal registers via I2C bus, then the camera supply pixel clock (PCLK) and camera data (Data[9:0]) back to the host with synchronize signal like HREF and VSYNC.

#### 2 M Pixels CMOS MT9D111 CAMERA MODULE

The host may have integrate camera interface like STM32F2 or STM32F4 series MCUs, or ARM9/11 which has dedicate camera port, and DPS like TI TMS320DM series, as well as FPGAs that user can design special logic for camera application. The typical connection between these system and camera module would show like following diagram.

For the host that doesn't have a dedicate camera interface, additional hardware is needed. User need to buffer a entire frame before read them out with low speed MCUs. For example ArduCAM shield is a additional hardware that can be connected to Arduino UNO/Mega board, user can take a photo or something like that easily. The following diagram show the system without dedicate camera interface.

### 5 Pin Definition

The MT9D111 module uses standard ArduCAM camera pin out. The pin number is listed as bellows.

| Pin No. | PIN NAME      | TYPE           | DESCRIPTION                                           |

|---------|---------------|----------------|-------------------------------------------------------|

| 1       | VCC           | POWER          | 3.3v Power supply                                     |

| 2       | GND           | Ground         | Power ground                                          |

| 3       | SCL           | Input          | Two-Wire Serial Interface Clock                       |

| 4       | SDATA         | Bi-directional | Two-Wire Serial Interface Data I/O                    |

| 5       | VSYNC         | Output         | Active High: Frame Valid; indicates active frame      |

| 6       | HREF          | Output         | Active High: Line/Data Valid; indicates active pixels |

| 7       | PCLK          | Output         | Pixel Clock output from sensor                        |

| 8       | XCLK          | Input          | Master Clock into Sensor                              |

| 9       | <b>D</b> оит7 | Output         | Pixel Data Output 7                                   |

| 10      | <b>D</b> оит6 | Output         | Pixel Data Output 6                                   |

| 11      | <b>D</b> оит5 | Output         | Pixel Data Output 5                                   |

| 12      | <b>D</b> оит4 | Output         | Pixel Data Output 4                                   |

| 13      | <b>D</b> оит3 | Output         | Pixel Data Output 3                                   |

| 14      | <b>D</b> оит2 | Output         | Pixel Data Output 2 (LSB)                             |

| 15      | <b>D</b> оит1 | Output         | Pixel Data Output 1(10bit mode)                       |

| 16      | <b>D</b> оит0 | Output         | Pixel Data Output 1(10bit mode)                       |

| 17      | GND           | Input          | Power down                                            |

| 18      | STB           | Input          | Standby, active high                                  |

| 19      | IR            | -              | Reserved                                              |

| 20      | RST           | Input          | Reset, active low                                     |

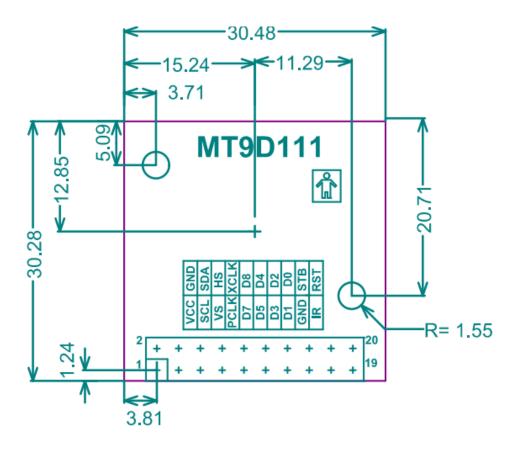

## **6** Mechanical Dimension